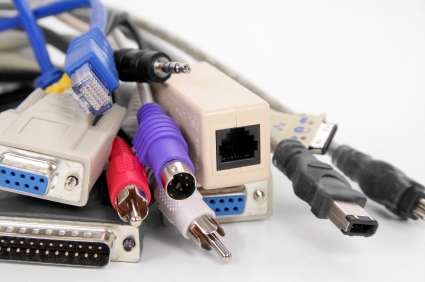

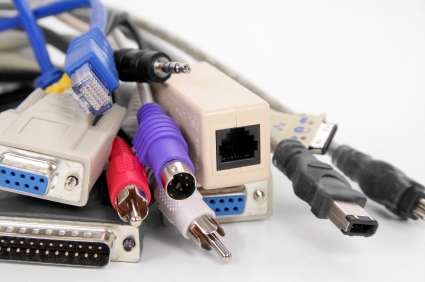

In Fig. These are all initialized to point at the first page for the moment. 3.1(a), for instance, the signal can be seen to vary over a fraction of a second. 3.1, which shows the varying analogue voltage signal (a) produced by an electronic thermometer over a period of 8 seconds, as it follows changes in temperature. ScienceDirect is a registered trademark of Elsevier B.V. ScienceDirect is a registered trademark of Elsevier B.V. . Flexibility. UML sequence diagram for data handling flow. Parallel ports require multiple data lines in their cables and ports to accomplish this. As can be seen from Fig. A discussion of computer data acquisition requires a clear appreciation of what the terms analogue and digital mean. This is because the hardware details are all encapsulated within the Hardware Proxy. Fig. The 01 bit patterns create the chirping sound characteristic of modems. IEEE 1149.7 also permits a star topology to be realized. The SIP has built-in network clock circuitry to receive and distribute clocking information between the Route Process (RP) and the SPAs. The system unit also includes the case that houses the internal components of the computer. Algorithmic complexity. The required instructions for all implementations include device bypass and boundary scan support (state sampling, register load, and internal and external test execution). NIUs (sometimes called network interfaces) are devices that serve as common interfaces for other devices within a local area network (LAN), or they are devices that allow networked computers to connect to outside networks. Continuously digitised input from auxiliary analogue channels is handled separately using a National Instruments interface card in the host computer. JTAG is a low-level hardware interface specified by IEEE Standard 1149 [11]. Table 8.1. When the energy goes above a threshold value, the appropriate bit is detected. Parallel ports are mostly used to connect printers to the system unit. Voltage samples are taken at regular intervals (every 0.25 s) during the time course of the signal and integer numbers assigned depending on the voltage interval each sample is found to lie within.

Sinusoidal tones are much better suited to transmission over analog phone lines than are the traditional high and low voltages of digital circuits. e.g. This results in the 32-sample digitised record shown in (c). rack mountable unit. Software emulations of these formats are easy to implement when the microcontrollers do not include the custom hardware peripherals required. Even though paravirtualization offers some unique advantages, there are many problems with the technology in general. It supports up to 128 channels with waveform digitisation handled by on-board Motorola digital signal processors, one for each bank of eight input channels. 3.1(c), 16 levels and only 32 samples are clearly insufficient to represent the smoothly varying time course of the original signal. Examples of paravirtualized platforms include the Xen and TRANGO hypervisors. What Is Harder The Math Or Computer Courses Computer Science? In a standard PC card installation, the controller downloads the MAC address directly from a flash EPROM during its reset sequence. It is also common in networking to hang more than two devices onto the same set of wires, in order to share the one line. The transmitting and receiving modems agree in advance on the length of time during which a bit will be transmitted (otherwise known as the baud rate). The continuous signal has also been quantised in terms of time, with information only available at the fixed times the samples were acquired. DB9 refers to a 9-pin connection, while DB25 refers to a 25-pin connection. Individual states may force normal operation, invoke test functions defined by the contents of the instruction register, pause testing, and perform capture, update, or logical shift of instruction or data register contents. CPUs have some basic limits on the rate at which they can process data. Two devices are connected together by an architecture. Thomas Sterling, Maciej Brodowicz, in High Performance Computing, 2018. Optionally the interface may also contain a TRST (test reset) signal to perform reset of the test logic. The basic purpose of the motherboard is to provide the electrical and logical connections by which the other components of the system communicate. To lower the required pin count, multiple JTAG-equipped devices may be daisy-chained as illustrated in Fig. We can expand on our requirements to identify several factors that influence the decision. In order to do this, the continuous range of possible analogue values must be converted into a corresponding range of discrete integer numbers. The software architecture of the ASR1000 router allows SPAs installed on the SIP to be hot-swapped individually, without impact to the remaining SPAs installed in the same SIP or the same chassis. The Cisco I-Flex design combines SPAs and SIPs. Digital means expressible in the form of numerical digits and a digital computer is one which stores and processes data in the form of numbers. JOHN DEMPSTER, in The Laboratory Computer, 2001. Receiving bits in the modem. An expansion port is any connector that passes data in and out of a computer or peripheral device.

What it also means is that one development group from company A has a version of the drivers but open source group B also has a set of drivers. Interfaces for computing hardware, such as SCSI, decouple the design and introduction of computing hardware, such as I/O devices, from the design and introduction of other components of a computing system, allowing users and manufacturers to implement computing systems in a more flexible manner. A USB port is a popular cable link interface for computers and other consumer electronics. The serial port on a computer is a form of a link for peripherals like mice, gaming controllers, modems, and older printers. The ISR should perform the minimum operations required to service the interrupt; other tasks can be performed in a software task that is under control of the operating system. An architecture used to interconnect two devices together. Read Great Stories Offline on Your Favorite, PC Magazine Digital Edition (Opens in a new window), How to Free Up Space on Your iPhone or iPad, How to Save Money on Your Cell Phone Bill, How to Convert YouTube Videos to MP3 Files, How to Record the Screen on Your Windows PC or Mac. All JTAG implementations must support the test access port (TAP) with the TCK, TMS, TDI, and TDO pins, TAP controller, at least a two-bit wide instruction register, a one-bit bypass register, and a boundary scan register (onebit or more). In both cases, we can reduce the chances for error by sending the waveforms for a longer time. Number representations with larger bit widths increase the size of hardware data paths. This gives a transmit allocation of 1664 bytes, big enough for a maximum size Ethernet frame. Thus, if there is any doubt over the appropriateness of the sampling rate, one should err on the side of higher rates. The major difference between these data acquisition systems lies, as it often does, in the software. 5.30.

Number representations with larger bit widths increase the size of hardware data paths. This gives a transmit allocation of 1664 bytes, big enough for a maximum size Ethernet frame. Thus, if there is any doubt over the appropriateness of the sampling rate, one should err on the side of higher rates. The major difference between these data acquisition systems lies, as it often does, in the software. 5.30.

Additionally, JTAG permits in-circuit debugging of embedded applications by being able to access most if not all of the device register state, including the status of I/O pins. CPU utilization. In the real world, however, most information is in analogue form inherently continuous and approximate in nature. One filter passes frequencies in the range that represents a 0 and rejects the 1-band frequencies, and the other filter does the converse. The modem will not implement a hardware interface to a telephone line or software for dialing a phone number. The receiving process is illustrated in Fig. For example, compressed or uncompressed digital data from an HDMI-compliant source device to a computer monitor, video projector, digital television, etc. Fig. Many issues arise in the choice of appropriate laboratory interface hardware and software, but at the heart of it is the basic principle of representing an analogue signal in digital form. Many devices will make use of the microcontroller's interrupt interface. ASR1000 Router Series SPA Interface Processor. 1996-2022 Ziff Davis. PCI Express (PCIe) slots, on the other hand, are sockets on the motherboard into which expansion cards are inserted. Note how the helper function nic_CmdRd(reg) is used to read one byte of data at a time from each register. Neuralynx provides a 160-channel system which also includes two additional channels designed to track the spatial position of a moving animal using a video camera. The remainder of the systems discussed here are designed more specifically for the challenge of acquiring large numbers (64128) of channels, the major suppliers for these being BionicTechnologies (Salt Lake City, UT, USA), Multi Channel Systems (Reutlingen, Germany), Neuralynx (Tucson, AZ, USA) and Plexon (Dallas, TX, USA). Numerical information is exact, in the sense that a number either does or does not have a particular value. An interface can be used to recognize events or to downsample the signals. However, a profound improvement in the quality of the signal can be obtained by using 256 digitisation levels and also increasing the number of samples to 98, as shown in Fig. In addition to the design of the plug and socket, the type, number, and purpose of the wires, and the electrical signals that pass through them, there are other details. It takes its name from the Joint Test Action Group, which in the mid-1980s set out to develop verification and test methods for electronic circuits. Either method is valid, and both are shown for demonstration purposes (only one is needed). Numerical precision and dynamic range. However, this degrades the maintainability of the system because now the clients need to be modified should the hardware interface or encoding change. As previously described, the SIP is built into the ASR1002 chassis and supported as a modular component on the Cisco ASR1004 and Cisco ASR1006 chassis options. Top 5 Benefits of Working Abroad, Interesting Ways Gyms are Incorporating Modern Technology, Why President Bidens Handling of Student Loans Might Impact Democratic Reelection Chances, Modern Ways People Are Getting Of Their Excessive Fat, How Are We Maintaining Our Apperance As We Age. Real-time spike sorting is handled by the DSPs. A parallel port is a type of interface found on computers (both personal and business) for connecting peripherals. This will be used for comparing against the address of incoming frames. Flexibility comes in several forms. Bionic Technologies can supply either a 16-channel system based upon standard hardware, or a 100-channel DSP-based system. Digital interfaces may provide low latency and analog interfaces can be highly responsive. A software routine may be changed after installation of the system. A computer interface can be classified into several different types. In some situations, and for some applications, there may be benefits in adding extra software functions to switch off the Ethernet interface, or to render it inactive. Copyright 2022 Elsevier B.V. or its licensors or contributors. document.getElementById( "ak_js_1" ).setAttribute( "value", ( new Date() ).getTime() ); Hacking In 2021: Topic of Ultimate Interest, Artificial Intelligence 2021: Best Innovation Of All Time, Internet: Biggest And Top Medium of World Wide Connection, Introduction, Features & Structure of C- Programming Language. The TAP controller embeds a predefined state machine with 16 states. Edward Insam PhD, BSc, in TCP/IP Embedded Internet Applications, 2003. (b) Quantisation levels (16) of a 4-bit ADC, over a 05 V range. The availability of ready made ICs makes the job much easier for the designer. Procedures for other devices will be rather similar, that is, writing a series of bytes to a number of registers in a specific order (see also section titled Initialization, Chapter 5). what is an interface in computer programming? These include transmit status, receive status, and various other flags. Since it can directly manipulate the device hardware state, JTAG is also occasionally used to perform firmware updates in cases when more user-friendly options may not be available or desirable. USB, FireWire, Ethernet, ATA/IDE, SCSI, and PCI are examples of USB. Instead, it runs the detection algorithm at the predicted middle of the bit. The first-generation SIP, both fixed and modular, supports up to 10Gbps throughout. We will also run at a much slower bit rate than 1200 baud tosimplify the implementation. Plexon's RASPUTIN package, particularly in terms of real-time spike sorting, seems to be the most comprehensive at present, with the analysis capabilities of the software supplied with some of the others often quite limited. This is used to ensure that the controller is present and is working properly. Some algorithms may be hard to implement as analog or digital circuits due to their size or the nature of the operations they perform. Given those understandings, let us fill out the requirements table. Ports are sometimes called jack or connectors. The code starts with a chip reset; the listing shows two alternative methods of resetting the chip, either by raising the reset pin high for a few milliseconds, or by writing a reset vector into one of the internal registers. It will normally be called once at the start of the program, although it should be possible to call it again at any time, maybe to re-initialize the hardware or after a catastrophic crash or major error. Data is transferred via an MXIbus parallel digital interface link between the MAP and the host computer. Figure 8.19(b) shows the Sort Client program from the RASPUTIN package used to set up the spike sorting and monitor the acquisition of data. Sample rate. A comparison of some neural spike data acquisition systems. Our expert industry analysis and practical solutions help you make better buying decisions and get more from technology. The display of third-party trademarks and trade names on this site does not necessarily indicate any affiliation or the endorsement of PCMag.

Sinusoidal tones are much better suited to transmission over analog phone lines than are the traditional high and low voltages of digital circuits. e.g. This results in the 32-sample digitised record shown in (c). rack mountable unit. Software emulations of these formats are easy to implement when the microcontrollers do not include the custom hardware peripherals required. Even though paravirtualization offers some unique advantages, there are many problems with the technology in general. It supports up to 128 channels with waveform digitisation handled by on-board Motorola digital signal processors, one for each bank of eight input channels. 3.1(c), 16 levels and only 32 samples are clearly insufficient to represent the smoothly varying time course of the original signal. Examples of paravirtualized platforms include the Xen and TRANGO hypervisors. What Is Harder The Math Or Computer Courses Computer Science? In a standard PC card installation, the controller downloads the MAC address directly from a flash EPROM during its reset sequence. It is also common in networking to hang more than two devices onto the same set of wires, in order to share the one line. The transmitting and receiving modems agree in advance on the length of time during which a bit will be transmitted (otherwise known as the baud rate). The continuous signal has also been quantised in terms of time, with information only available at the fixed times the samples were acquired. DB9 refers to a 9-pin connection, while DB25 refers to a 25-pin connection. Individual states may force normal operation, invoke test functions defined by the contents of the instruction register, pause testing, and perform capture, update, or logical shift of instruction or data register contents. CPUs have some basic limits on the rate at which they can process data. Two devices are connected together by an architecture. Thomas Sterling, Maciej Brodowicz, in High Performance Computing, 2018. Optionally the interface may also contain a TRST (test reset) signal to perform reset of the test logic. The basic purpose of the motherboard is to provide the electrical and logical connections by which the other components of the system communicate. To lower the required pin count, multiple JTAG-equipped devices may be daisy-chained as illustrated in Fig. We can expand on our requirements to identify several factors that influence the decision. In order to do this, the continuous range of possible analogue values must be converted into a corresponding range of discrete integer numbers. The software architecture of the ASR1000 router allows SPAs installed on the SIP to be hot-swapped individually, without impact to the remaining SPAs installed in the same SIP or the same chassis. The Cisco I-Flex design combines SPAs and SIPs. Digital means expressible in the form of numerical digits and a digital computer is one which stores and processes data in the form of numbers. JOHN DEMPSTER, in The Laboratory Computer, 2001. Receiving bits in the modem. An expansion port is any connector that passes data in and out of a computer or peripheral device.

What it also means is that one development group from company A has a version of the drivers but open source group B also has a set of drivers. Interfaces for computing hardware, such as SCSI, decouple the design and introduction of computing hardware, such as I/O devices, from the design and introduction of other components of a computing system, allowing users and manufacturers to implement computing systems in a more flexible manner. A USB port is a popular cable link interface for computers and other consumer electronics. The serial port on a computer is a form of a link for peripherals like mice, gaming controllers, modems, and older printers. The ISR should perform the minimum operations required to service the interrupt; other tasks can be performed in a software task that is under control of the operating system. An architecture used to interconnect two devices together. Read Great Stories Offline on Your Favorite, PC Magazine Digital Edition (Opens in a new window), How to Free Up Space on Your iPhone or iPad, How to Save Money on Your Cell Phone Bill, How to Convert YouTube Videos to MP3 Files, How to Record the Screen on Your Windows PC or Mac. All JTAG implementations must support the test access port (TAP) with the TCK, TMS, TDI, and TDO pins, TAP controller, at least a two-bit wide instruction register, a one-bit bypass register, and a boundary scan register (onebit or more). In both cases, we can reduce the chances for error by sending the waveforms for a longer time.

Number representations with larger bit widths increase the size of hardware data paths. This gives a transmit allocation of 1664 bytes, big enough for a maximum size Ethernet frame. Thus, if there is any doubt over the appropriateness of the sampling rate, one should err on the side of higher rates. The major difference between these data acquisition systems lies, as it often does, in the software. 5.30.

Number representations with larger bit widths increase the size of hardware data paths. This gives a transmit allocation of 1664 bytes, big enough for a maximum size Ethernet frame. Thus, if there is any doubt over the appropriateness of the sampling rate, one should err on the side of higher rates. The major difference between these data acquisition systems lies, as it often does, in the software. 5.30. Additionally, JTAG permits in-circuit debugging of embedded applications by being able to access most if not all of the device register state, including the status of I/O pins. CPU utilization. In the real world, however, most information is in analogue form inherently continuous and approximate in nature. One filter passes frequencies in the range that represents a 0 and rejects the 1-band frequencies, and the other filter does the converse. The modem will not implement a hardware interface to a telephone line or software for dialing a phone number. The receiving process is illustrated in Fig. For example, compressed or uncompressed digital data from an HDMI-compliant source device to a computer monitor, video projector, digital television, etc. Fig. Many issues arise in the choice of appropriate laboratory interface hardware and software, but at the heart of it is the basic principle of representing an analogue signal in digital form. Many devices will make use of the microcontroller's interrupt interface. ASR1000 Router Series SPA Interface Processor. 1996-2022 Ziff Davis. PCI Express (PCIe) slots, on the other hand, are sockets on the motherboard into which expansion cards are inserted. Note how the helper function nic_CmdRd(reg) is used to read one byte of data at a time from each register. Neuralynx provides a 160-channel system which also includes two additional channels designed to track the spatial position of a moving animal using a video camera. The remainder of the systems discussed here are designed more specifically for the challenge of acquiring large numbers (64128) of channels, the major suppliers for these being BionicTechnologies (Salt Lake City, UT, USA), Multi Channel Systems (Reutlingen, Germany), Neuralynx (Tucson, AZ, USA) and Plexon (Dallas, TX, USA). Numerical information is exact, in the sense that a number either does or does not have a particular value. An interface can be used to recognize events or to downsample the signals. However, a profound improvement in the quality of the signal can be obtained by using 256 digitisation levels and also increasing the number of samples to 98, as shown in Fig. In addition to the design of the plug and socket, the type, number, and purpose of the wires, and the electrical signals that pass through them, there are other details. It takes its name from the Joint Test Action Group, which in the mid-1980s set out to develop verification and test methods for electronic circuits. Either method is valid, and both are shown for demonstration purposes (only one is needed). Numerical precision and dynamic range. However, this degrades the maintainability of the system because now the clients need to be modified should the hardware interface or encoding change. As previously described, the SIP is built into the ASR1002 chassis and supported as a modular component on the Cisco ASR1004 and Cisco ASR1006 chassis options. Top 5 Benefits of Working Abroad, Interesting Ways Gyms are Incorporating Modern Technology, Why President Bidens Handling of Student Loans Might Impact Democratic Reelection Chances, Modern Ways People Are Getting Of Their Excessive Fat, How Are We Maintaining Our Apperance As We Age. Real-time spike sorting is handled by the DSPs. A parallel port is a type of interface found on computers (both personal and business) for connecting peripherals. This will be used for comparing against the address of incoming frames. Flexibility comes in several forms. Bionic Technologies can supply either a 16-channel system based upon standard hardware, or a 100-channel DSP-based system. Digital interfaces may provide low latency and analog interfaces can be highly responsive. A software routine may be changed after installation of the system. A computer interface can be classified into several different types. In some situations, and for some applications, there may be benefits in adding extra software functions to switch off the Ethernet interface, or to render it inactive. Copyright 2022 Elsevier B.V. or its licensors or contributors. document.getElementById( "ak_js_1" ).setAttribute( "value", ( new Date() ).getTime() ); Hacking In 2021: Topic of Ultimate Interest, Artificial Intelligence 2021: Best Innovation Of All Time, Internet: Biggest And Top Medium of World Wide Connection, Introduction, Features & Structure of C- Programming Language. The TAP controller embeds a predefined state machine with 16 states. Edward Insam PhD, BSc, in TCP/IP Embedded Internet Applications, 2003. (b) Quantisation levels (16) of a 4-bit ADC, over a 05 V range. The availability of ready made ICs makes the job much easier for the designer. Procedures for other devices will be rather similar, that is, writing a series of bytes to a number of registers in a specific order (see also section titled Initialization, Chapter 5). what is an interface in computer programming? These include transmit status, receive status, and various other flags. Since it can directly manipulate the device hardware state, JTAG is also occasionally used to perform firmware updates in cases when more user-friendly options may not be available or desirable. USB, FireWire, Ethernet, ATA/IDE, SCSI, and PCI are examples of USB. Instead, it runs the detection algorithm at the predicted middle of the bit. The first-generation SIP, both fixed and modular, supports up to 10Gbps throughout. We will also run at a much slower bit rate than 1200 baud tosimplify the implementation. Plexon's RASPUTIN package, particularly in terms of real-time spike sorting, seems to be the most comprehensive at present, with the analysis capabilities of the software supplied with some of the others often quite limited. This is used to ensure that the controller is present and is working properly. Some algorithms may be hard to implement as analog or digital circuits due to their size or the nature of the operations they perform. Given those understandings, let us fill out the requirements table. Ports are sometimes called jack or connectors. The code starts with a chip reset; the listing shows two alternative methods of resetting the chip, either by raising the reset pin high for a few milliseconds, or by writing a reset vector into one of the internal registers. It will normally be called once at the start of the program, although it should be possible to call it again at any time, maybe to re-initialize the hardware or after a catastrophic crash or major error. Data is transferred via an MXIbus parallel digital interface link between the MAP and the host computer. Figure 8.19(b) shows the Sort Client program from the RASPUTIN package used to set up the spike sorting and monitor the acquisition of data. Sample rate. A comparison of some neural spike data acquisition systems. Our expert industry analysis and practical solutions help you make better buying decisions and get more from technology. The display of third-party trademarks and trade names on this site does not necessarily indicate any affiliation or the endorsement of PCMag.